This sections shows a basic multiply-accumulate design in Simulink. Generating HDL and the Cosimulation Model Specific makehdltb examples are given for those simulators at the end. The main examples show using Mentor Graphics® ModelSim®/Questa®, but other supported simulators include Cadence® Xcelium™ (formerly Incisive®) and Xilinx® Vivado™ Simulator.

The end result is a cosimulation model that is ready to verify the generated code. All of the automated settings are documented in the generated scripts. The automated cosimulation model generation takes the guess-work out of the HDL cosimulation block and simulator setup by deciphering all the compiled model and code generation information. It is important to keep in-sync various aspects of the source model including sample rates, feedforward/feedthrough systems, and other various parameters and settings used during code generation, while setting up the HDL Verifier cosimulation block and the target HDL simulator.

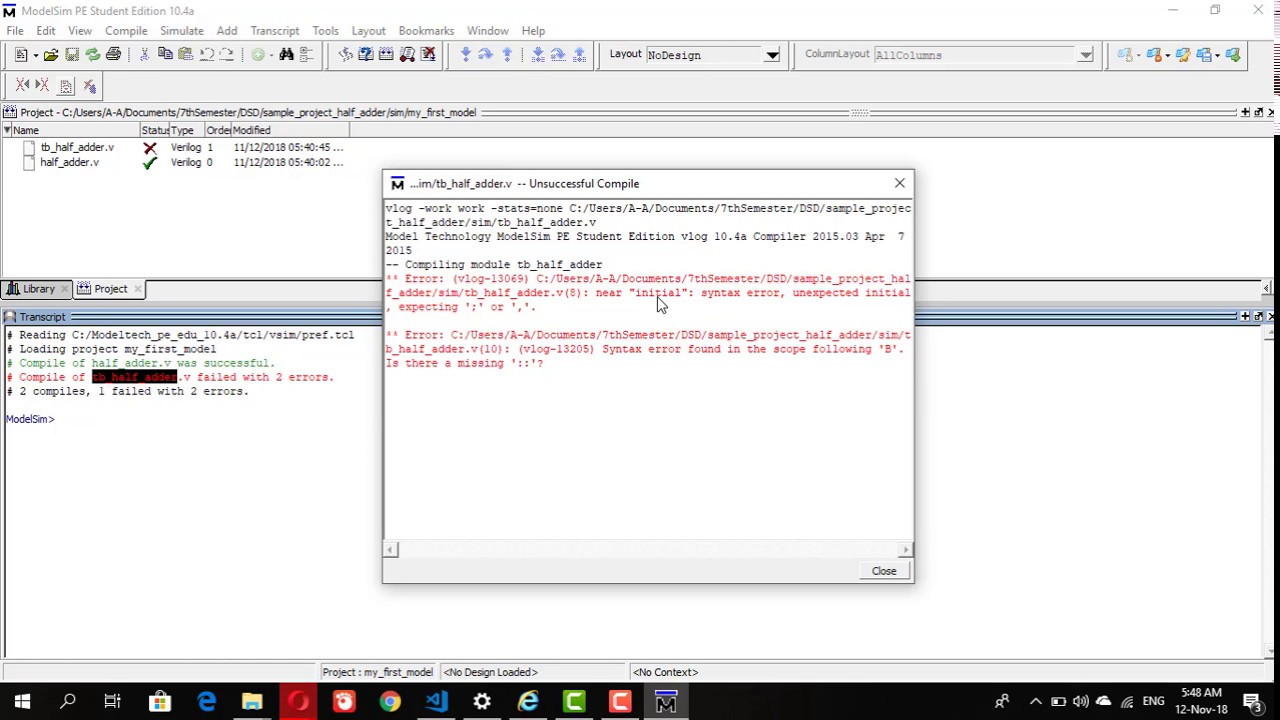

Cosimulation is a challenging task, especially with automatically generated code.

0 kommentar(er)

0 kommentar(er)